LLVM начинает подготовку к использованию процессоров Intel Sierra Forest и Grand Ridge

На прошлой неделе Intel разослала новые исправления компилятора GCC для добавления целевого процессора «Sierra Forest» и количества новых инструкций x86_64, которые она добавляет. Эти исправления GCC последовали за тем, как Intel опубликовала обновленное справочное руководство по программированию, в котором они подробно описали эти новые инструкции для процессоров Sierra Forest Xeon, а также Grand Ridge. Что касается компилятора LLVM, они также начали выпускать новые исправления для этих новых инструкций Intel.

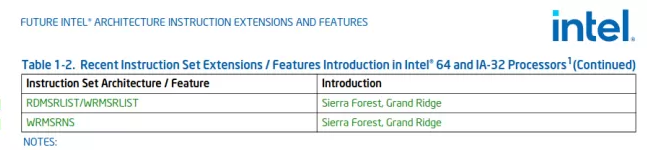

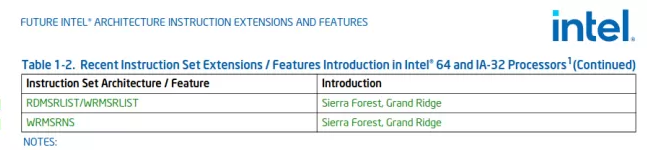

Первая работа по внедрению Sierra Forest / Grand Ridge, которая в одночасье приземлилась в LLVM 16, — это добавление инструкций WRMSRNS и инструкций MSRLIST — новых для Sierra Forest и Grand Ridge.

Инструкции MSRLIST — это RDMSRLIST для чтения списка регистров, специфичных для модели, и WRMSRLIST для записи списка регистров, специфичных для модели. Эти новые инструкции RDMSRLIST/WRMSRLIST позволяют одновременно предоставлять список до 64 регистров конкретной модели с помощью этой инструкции по сравнению с инструкциями RDMSR/WRMSR, которые одновременно являются MSR.

На данный момент в LLVM также добавлен WRMSRNS. WRMSRNS с Grand Ridge и Sierra Forest — это запись без сериализации в регистр конкретной модели. Вместо того, чтобы WRMSR была сериализованной инструкцией, WRMSRNS представляет собой несериализующую запись, но в остальном ведет себя так же.

В обновлении справочного руководства по программированию Intel, выпущенном в прошлом месяце, также упоминается еще несколько инструкций, поставляемых с Sierra Forest и Ridge Ridge, включая CMPCCXADD, AVX-IFMA, AVX-NE-CONVERT и AVX-VNNI-INT8. Пока что эти дополнительные инструкции не попали ни в LLVM Git, ни в цель «-march=sierraforest», но, учитывая обычную пунктуальность Intel в отношении исправлений компилятора, они, вероятно, скоро появятся. Эти части, вероятно, не будут выпущены до 2024 года, а LLVM Git еще не видел каких-либо целей AMD Zen 4 (znver4) и настроенной поддержки, добавленной для этих уже поставляемых процессоров.

Первая работа по внедрению Sierra Forest / Grand Ridge, которая в одночасье приземлилась в LLVM 16, — это добавление инструкций WRMSRNS и инструкций MSRLIST — новых для Sierra Forest и Grand Ridge.

Инструкции MSRLIST — это RDMSRLIST для чтения списка регистров, специфичных для модели, и WRMSRLIST для записи списка регистров, специфичных для модели. Эти новые инструкции RDMSRLIST/WRMSRLIST позволяют одновременно предоставлять список до 64 регистров конкретной модели с помощью этой инструкции по сравнению с инструкциями RDMSR/WRMSR, которые одновременно являются MSR.

На данный момент в LLVM также добавлен WRMSRNS. WRMSRNS с Grand Ridge и Sierra Forest — это запись без сериализации в регистр конкретной модели. Вместо того, чтобы WRMSR была сериализованной инструкцией, WRMSRNS представляет собой несериализующую запись, но в остальном ведет себя так же.

В обновлении справочного руководства по программированию Intel, выпущенном в прошлом месяце, также упоминается еще несколько инструкций, поставляемых с Sierra Forest и Ridge Ridge, включая CMPCCXADD, AVX-IFMA, AVX-NE-CONVERT и AVX-VNNI-INT8. Пока что эти дополнительные инструкции не попали ни в LLVM Git, ни в цель «-march=sierraforest», но, учитывая обычную пунктуальность Intel в отношении исправлений компилятора, они, вероятно, скоро появятся. Эти части, вероятно, не будут выпущены до 2024 года, а LLVM Git еще не видел каких-либо целей AMD Zen 4 (znver4) и настроенной поддержки, добавленной для этих уже поставляемых процессоров.

Похожие публикации

Нет комментариев